Securyzr™ Network Security Crypto Accelerator

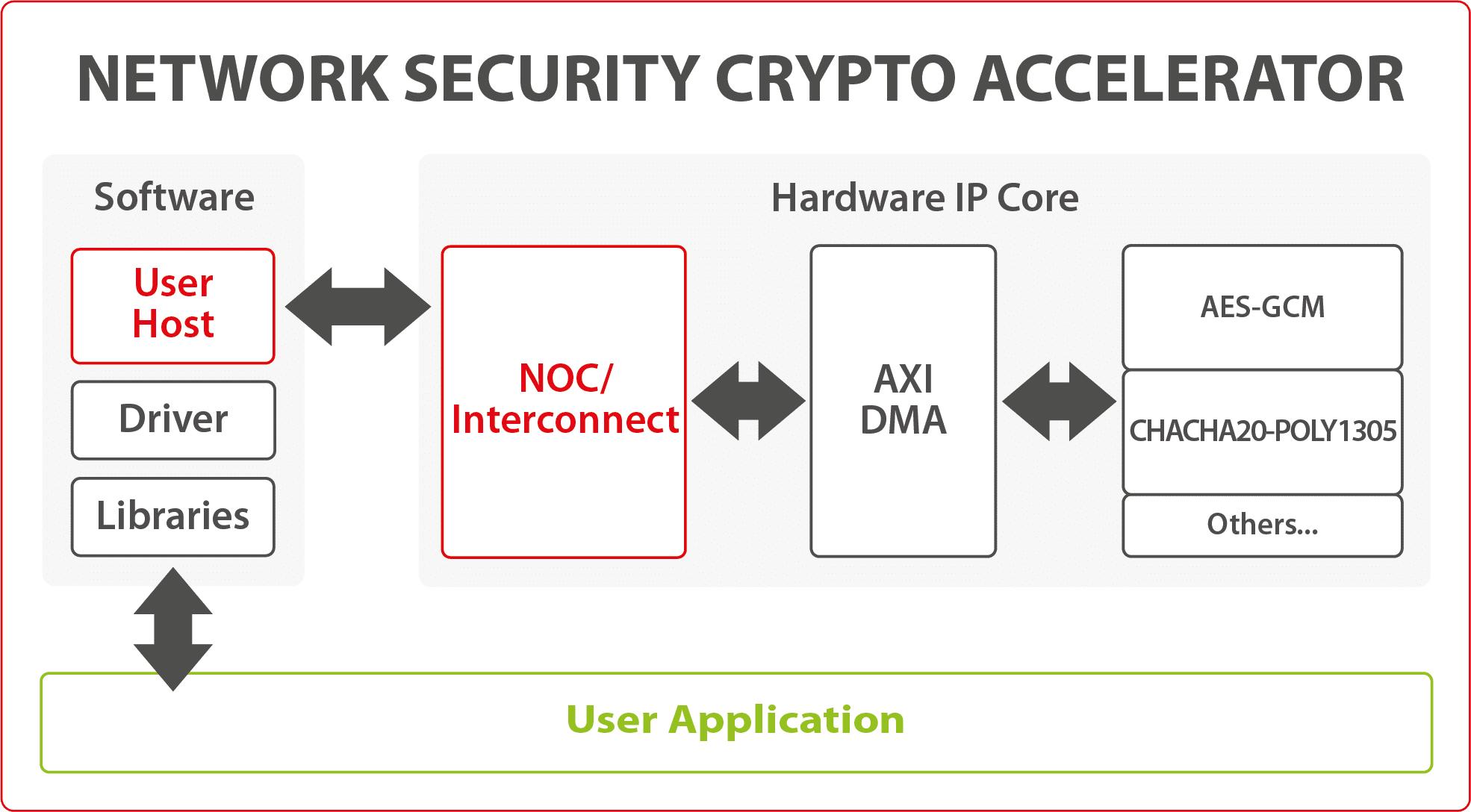

Accelerates cryptographic operations in System-on-Chip (SoC) environment on FPGA or ASIC.

To answer the needs of high-performance systems, a new generation of powerful processors is being designed and deployed. These multi-core SoCs contain dedicated hardware accelerators that offload challenging tasks, such as network protocol computation, AI and deep learning, and – most importantly – security. For a security performance that matches the speed of the new SoCs we have developed a scalable hardware IP block that handles encryption at speeds from a few Gbps to over 100Gbps, depending on the needs.

The Network Security Crypto Accelerator is used to accelerate/offload MACsec, IPsec, VPN, TLS/SSL, disk encryption, or any other custom application, requiring symmetric cryptography algorithms. It can also be combined with the eSecure Root of Trust module to form a complete secure enclave, that will handle the keys without exposing them to the software, which makes it suited for even the most regulated and security-sensitive industries.

Features

Applications

The Network Security Crypto Accelerator will bring the most efficient and flexible solution to your needs, whatever technology and architecture you choose.

Includes Direct Memory Interface

|

Native speeds of hardware cores may remain largely theoretical if the host processor is not able to deliver data to the crypto module and process the results at the same speed. That is why this Network Security Crypto Accelerator includes a Direct Memory Access (DMA) interface to the host memory space. Here, the operations are efficiently offloaded via a built-in scatter-gather DMA optimized to handle networks packets of any size. |

|

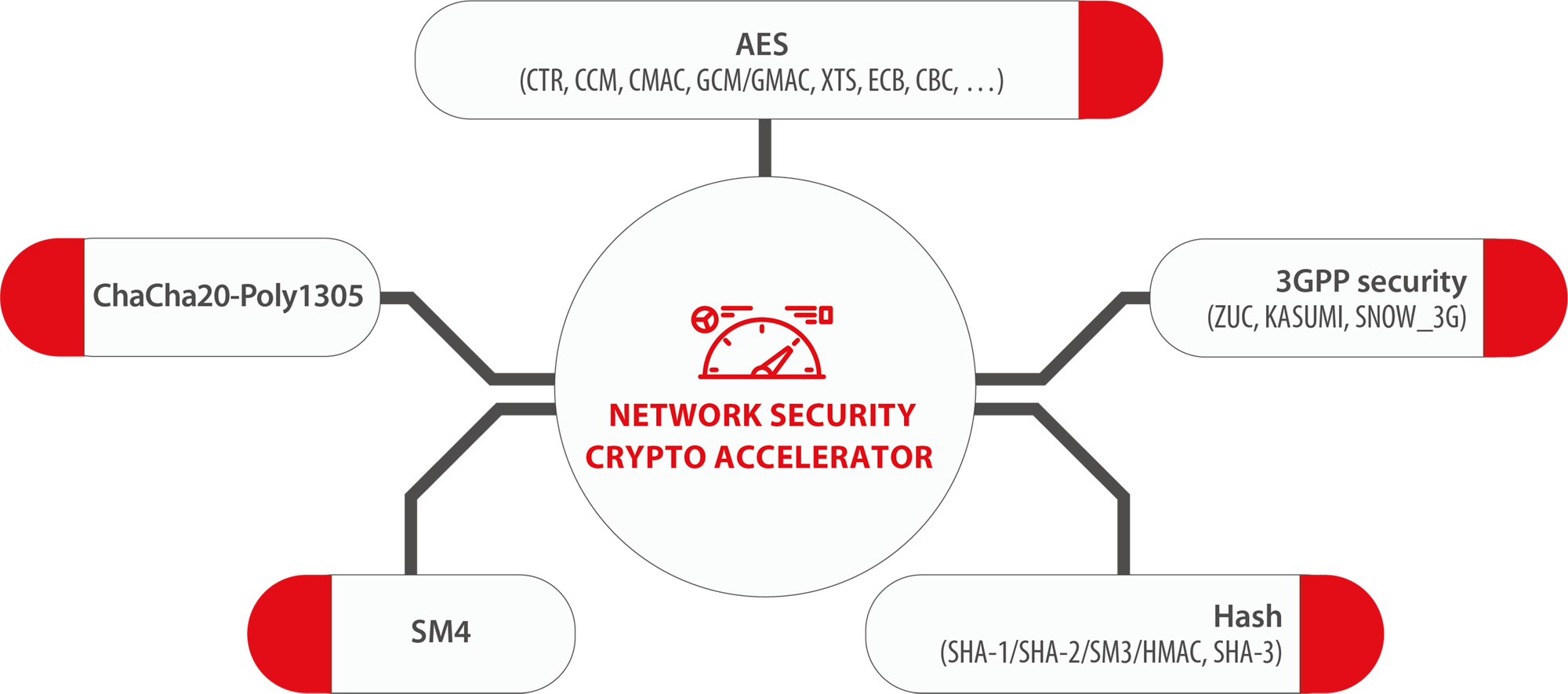

Crypto engines integration

The following cryptographic engines can be selected to be integrated:

Other high performance IP blocks to offload network & security processin

Can be used in combination with the Network Security Crypto Accelerator

We are offering the key components to boost your data center, including one of the fastest SSL/TLS handshaking engines for asymmetric operations in the industry and ultra-high performance MACsec and IPsec processing.

|

TLS Handshake Hardware Accelerator (SCZ_SP_BA452) An asymmetric secure connection engine that can be used to offload the compute intensive Public Key operations. |

|

|

MACsec Engine (SCZ_SP_BA451) Providing connectionless data integrity, data origin authenticity and confidentiality on OSI layer 2. |

|

|

IPsec Engine (SCZ_SP_BA454) Providing confidentiality, connectionless data integrity, data-origin authentication and replay protection on OSI layer 3. |

The first worldwide PQC READY secure solution from chip to cloud

|

At Secure-IC we are at the forefront of PQC, meaning we are actively working on developing and implementing PQC technologies, and contributing to the advancement of the field. We are conducting research, creating new PQC algorithms, developing PQC-based products, and working with customers to integrate PQC solutions into their systems. |