Securyzr™ TLS Handshake Hardware Accelerator

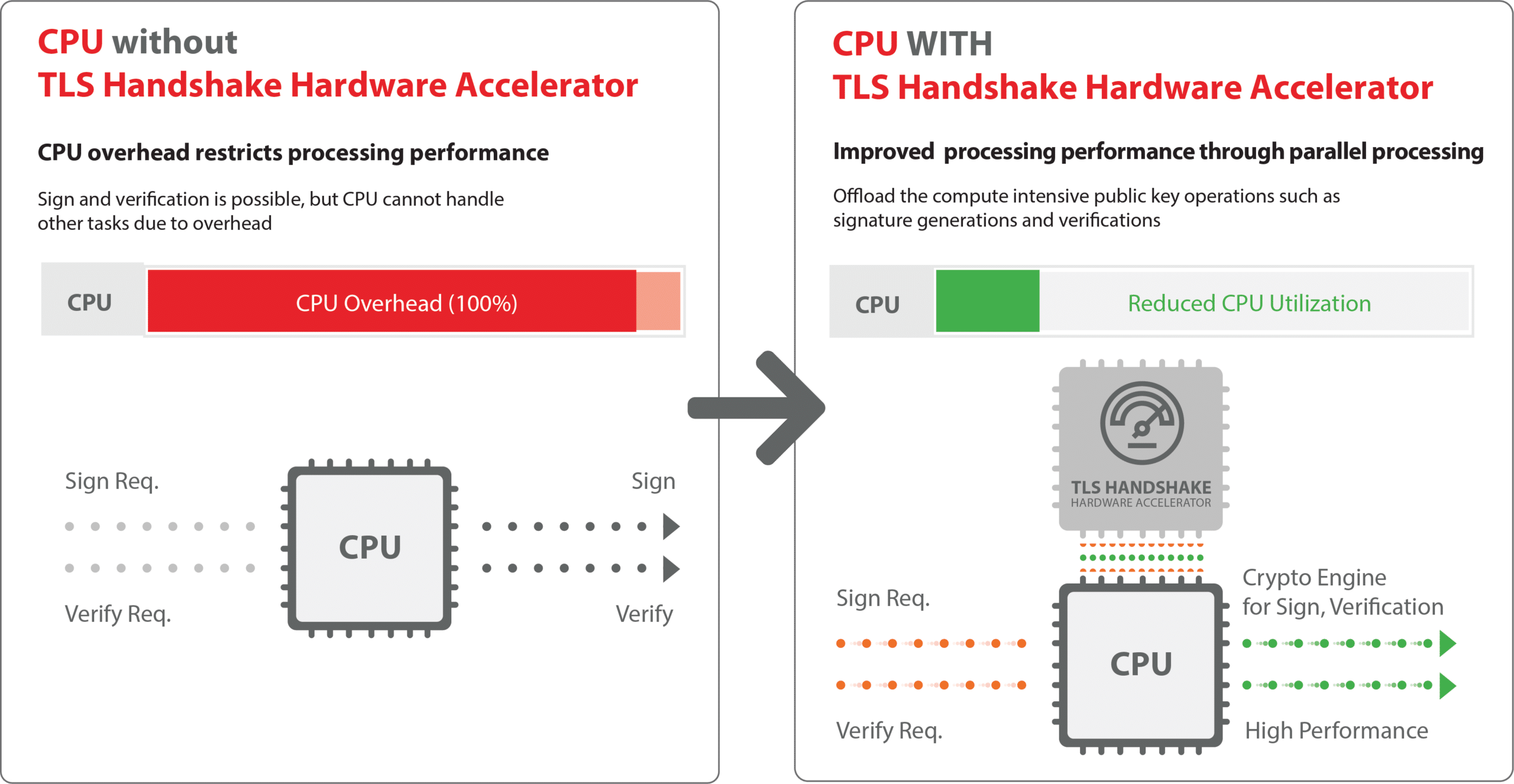

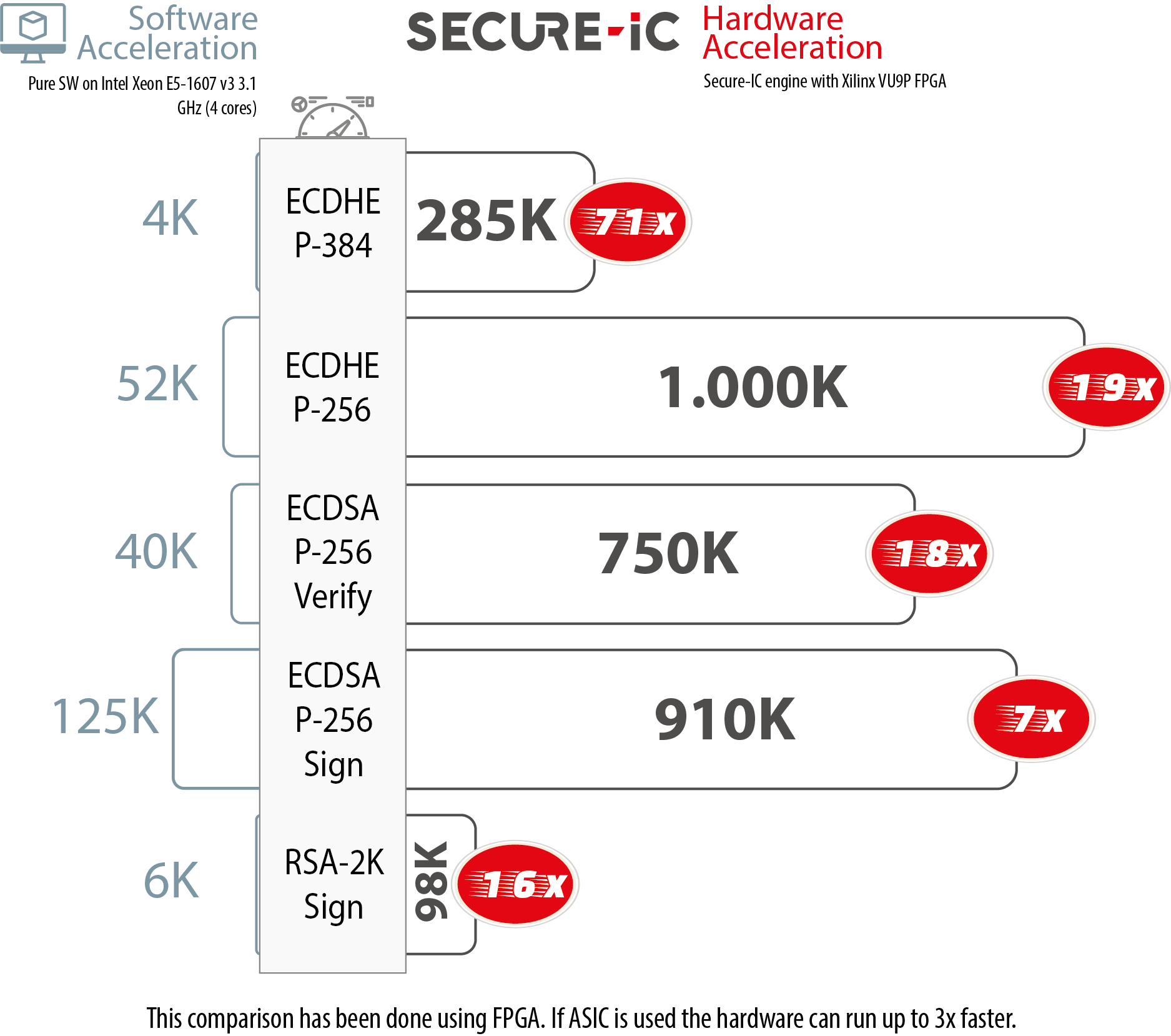

Offloads the compute intensive public key operations such as signature generations and verifications.

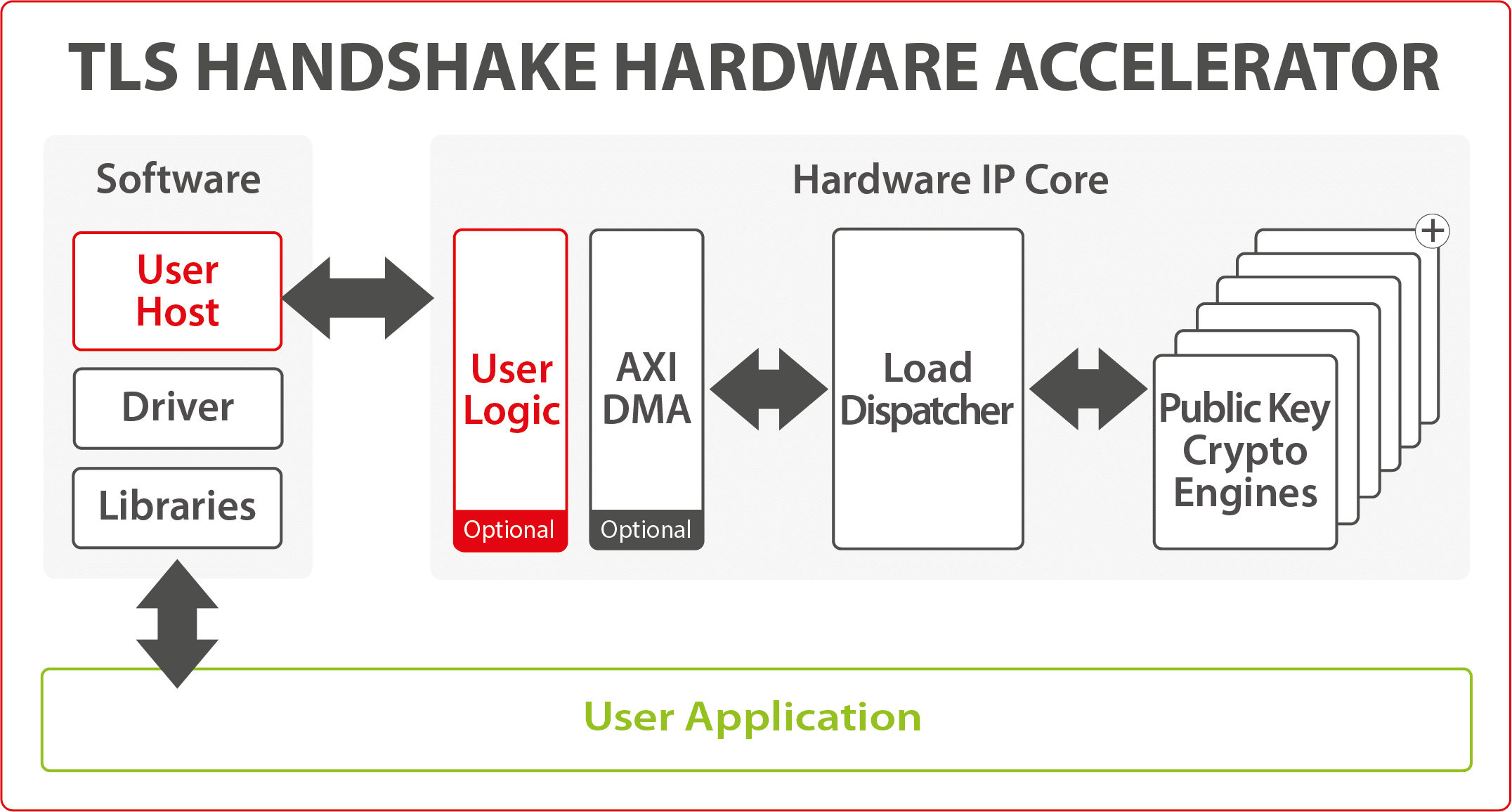

The TLS Handshake Hardware Accelerator combines a load dispatcher and a configurable amount of instances of the Public Key Crypto Engine, benefiting from all features supported (i.e. RSA / DH / DHE and ECDSA / ECDH / ECDH E / X.25519 / X.448 and more).

The efficient dispatching to several tenths of Public Key Crypto Engine instances helps reaching maximum system performance.

WHY TLS Handshake Hardware Accelerator?

Huge reduction for cpu overhead & incredible improvement for work processing efficiency

| High scalability | ||

| Trade-off between throughput, area and latency | ||

| Optimal performance for any application regardless of the platform on which the solution is implemented | ||

| Easy porting to ASIC and FPGA | ||

| Support of a wide range of applications in cloud computing and data centers |

Features

Free white paper

HOW SMART & SECURE HARDWARE

CAN BOOST YOUR DATA CENTER

High-performance IP blocks to offload network and security processing

Cloud computing is ramping up like never before. New host applications are routinely designed to serve millions of clients, and each of these clients expects high-speed service, minimal latency, and tight security.

Learn more about the key components to boost your data center:

• Record-breaking MACsec performance (up to 1.5Tbps)

• The fastest SSL/TLS handshaking engines in the industry

• …and much more

The first worldwide PQC READY secure solution from chip to cloud

|

At Secure-IC we are at the forefront of PQC, meaning we are actively working on developing and implementing PQC technologies, and contributing to the advancement of the field. We are conducting research, creating new PQC algorithms, developing PQC-based products, and working with customers to integrate PQC solutions into their systems. |